Общие сведения[]

В целом поддержка отладки не является обязательной; кроме того, возможный уровень отладки зависит от версии архитектуры (так, ARMv6-M не предусматривает возможности трассировки выполнения программы).

Регистры, управляющие отладочными средствами и отражающие их состояние, распределены между следующими устройствами на PPB:

- блоком управления системой (регистр DFSR, описанный, в отличие от других регистров SCB, в этом разделе);

- блоком управления отладкой (DCB, debug control block);

- блоком трассировки и слежения за данными (DWT, debug watchpoint and trace);

- блоком точек останова (BPU, breakpoint unit);

- таблицей ПЗУ (ROM table).

Все отладочные компоненты стандартизированы спецификацией ARM CoreSight. Каждый из них занимает один или несколько смежных 4-килобайтовых блоков адресного пространства. Последние адреса последнего блока адресного пространства компонента заняты стандартными регистрами Coresight, к которым относятся, в частности, регистры идентификации периферийного устройства и компонента, позволяющие однозначно определить данный компонент.

Помимо описанных в этом разделе регистров, при отладке могут использоваться некоторые другие регистры, например, регистр SHCSR. Однако эти регистры фактически используются не отладчиком как таковым, а программистом, осуществляющим отладку, для выполнения некоторых специфических операций (например, для принудительного сброса ожидающего условия прерывания).

Отладчик обращается к отладочным регистрам через порт отладочного доступа (DAP, debug access port). ARM делит DAP на две части: отладочный порт (DP), обеспечивающий подключение внешнего отладчика, и порт доступа (AP), позволяющий получить доступ к шине, к которой подключены отладочные компоненты. Отладчик, подключённый к DP, через него обращается к AP, а последний обеспечивает доступ к отладочным компонентам. Среди аппаратных ресурсов AP, доступных отладчику, имеется регистр, содержащий адрес таблицы ПЗУ верхнего уровня, которая является исходной точкой для определения топологии отладочных средств.

Имеет ли доступ к большей части отладочных регистров только отладчик или же они доступны и процессору, определяется реализацией. Как правило, в процессорах M-профиля для их упрощения и удешевления и DAP, и процессор для обращения к регистрам используют физически одну и ту же шину, и поэтому процессор может обращаться к отладочным регистрам наравне с отладчиком.

Доступ к отладочным регистрам возможен только в привилегированном состоянии и должен производиться выровненными словами.

Согласно документации, у большинства регистров нет отдельных версий для безопасного и небезопасного состояний, однако та же самая документация указывает на возможность обращения безопасного кода к небезопасной версии регистра по отдельному адресу. Вероятно, на самом деле безопасный код может использовать два адреса для обращения к одному и тому же регистру, а небезопасный, а также отладчик — только один (их обращение по второму адресу для считывания возвращает нули, а запись игнорируется). Потенциально это даёт возможность в будущем расширить функционал, введя отдельные версии регистров для разных режимов безопасности, но сохранив совместимость с существующим кодом.

Регистры SCB и DCB[]

Регистр состояния отладочных отказов DFSR[]

Назначение

- Показывает наступившие отладочные события.

Ограничения на использование

- Только привилегированный доступ (отказ при попытке непривилегированного доступа).

- Доступ только к целому слову (непредсказуемый результат при доступе к полуслову или байту).

- В версии ARMv8-M без основного расширения и в ARMv6-M доступность для программы определяется реализацией; в остальных вариантах доступ для программы имеется всегда.

- В версии ARMv8.1-M DAP может использовать непривилегированные доступы к этому регистру, если установлен бит DAUTHCTRL.UIDAPEN для любого из режимов безопасности.

Конфигурации

- В ARMv8-M без основного расширения и в ARMv6-M имеется только при поддержке отладки (при её отсутствии считывается и записывается как нуль); в ARMv8-M с основным расширением и ARMv7-M имеется всегда.

Атрибуты

- Адрес E000ED30, доступ на чтение и запись (запись единицы сбрасывает соответствующий разряд).

- Небезопасная версия доступна безопасному коду по адресу E002ED30.

- Регистр не имеет отдельных экземпляров для безопасного и небезопасного состояний.

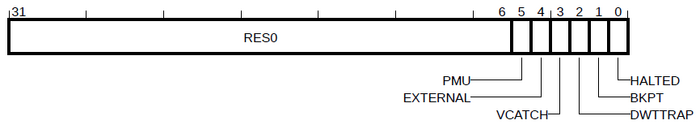

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервировано. | |||

| Этот бит установлен, если наступило событие PMU, и сброшен в противном случае.

Реализован только начиная с ARMv8.1-M при наличии PMU. Холодным сбросом обнуляется. | |||

| Этот бит установлен, если поступил внешний запрос на отладку.

Холодным сбросом обнуляется. | |||

| Этот бит установлен, если произошло событие совпадения вектора (vector catch).

Равен нулю, если отладочные остановы не поддерживаются. Холодным сбросом обнуляется. | |||

| Этот бит установлен, если произошло событие слежения за данными (watchpoint).

Равен нулю, если DWT отсутствует. Холодным сбросом обнуляется. | |||

| Этот бит установлен, если встречена точка останова (breakpoint).

Холодным сбросом обнуляется. | |||

| Этот бит установлен, если произошло событие отладочного останова или отладочного шага. Его значение непредсказуемо, если регистр считывается командой, выполняемой в пошаговом режиме.

Холодным сбросом обнуляется. |

Регистр управления аутентификацией отладки DAUTHCTRL[]

Назначение

- Обеспечивает возможность программного переопределения работы интерфейса аутентификации, определяемого реализацией.

Ограничения на использование

- Только привилегированный доступ (отказ при непривилегированном доступе).

- Для версии ARMv8.1-M доступы возможны байтами, полусловами и целым словом.

- Отладчик доступа не имеет (регистр считывается как 0, запись игнорируется).

Конфигурации

- Появился в ARMv8-M.

- Имеется только при поддержке отладки с остановом или основного расширения, в противном случае считывается как 0, а запись игнорируется.

Атрибуты

- Адрес E000EE04.

- При наличии расширения безопасности для доступа безопасного кода к небезопасной версии регистра используется адрес E002EE04, который считывается и записывается как нуль для небезопасного кода и для отладчика.

- Биты UIDEN и UIDAPEN реализованы отдельно для безопасного и небезопасного состояний, остальные биты реализованы только для безопасного состояния.

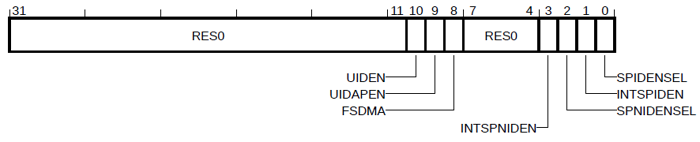

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервировано. | |||

Разрешение отладки непривилегированного кода:

В версиях до ARMv8.1-M и при отсутствии UDE заверзервирован и равен нулю. Этот бит имеет безопасную и небезопасную версии. Установка бита безопасного режима разрешает отладку непривилегированного кода как в безопасном, так и в небезопасном режиме, бита небезопасного режима – только в небезопасном режиме. При тёплом сбросе обнуляется. | |||

Разрешение непривилегированных доступов со стороны DAP:

В версиях до ARMv8.1-M и при отсутствии UDE заверзервирован и равен нулю. Этот бит имеет безопасную и небезопасную версии. Непривилегированные доступы DAP разрешаются, если установлен хотя бы один из этих двух битов. При холодном сбросе обнуляется. | |||

Принудительное разрешение безопасного прерывания DebugMonitor даже если отладочный останов в безопасном режиме запрещён:

В версиях до ARMv8.1-M заверзервирован и равен нулю. Имеется только безопасная версия этого бита; при обращении небезопасного кода считывается нуль, а запись игнорируется. При тёплом сбросе обнуляется. | |||

| Зарезервировано. | |||

Разрешение неинвазивной отладки безопасного режима:

Переопределяет разрешение, поступающее от внешнего интерфейса аутентификцаии. Игнорируется, если бит SPNIDENSEL сброшен. Имеется только безопасная версия этого бита; при обращении небезопасного кода считывается нуль, а запись игнорируется. При холодном сбросе обнуляется. | |||

Выбор способа разрешения неинвазивной отладки безопасного режима:

Состояние этого бита и внешнего интерфейса игнорируется при установленном бите DHCSR_S.S_SDE. Имеется только безопасная версия этого бита; при обращении небезопасного кода считывается нуль, а запись игнорируется. При холодном сбросе обнуляется. | |||

Разрешение инвазивной отладки безопасного режима:

Переопределяет разрешение, поступающее от внешнего интерфейса аутентификцаии. Игнорируется, если бит SPIDENSEL сброшен. Имеется только безопасная версия этого бита; при обращении небезопасного кода считывается нуль, а запись игнорируется. При холодном сбросе обнуляется. | |||

Выбор способа разрешения инвазивной отладки безопасного режима:

Имеется только безопасная версия этого бита; при обращении небезопасного кода считывается нуль, а запись игнорируется. При холодном сбросе обнуляется. |

Регистр состояния и управления отладочными остановами DHCSR[]

Назначение

- Управляет отладкой.

Ограничения на использование

- Только привилегированный доступ (отказ при непривилегированном доступе).

- Доступ только к слову (непредсказуемый результат при доступе к полуслову или байту).

- Начиная с ARMv8.1-M, при установке бита DAUTHCTRL.UIDAPEN для любого режима безопасности возможны непривилегированные доступы от DAP.

- Доступность для программы определяется реализацией (при отсутствии доступа считывается и записывается нуль).

Конфигурации

- Имеется только при поддержке отладки с остановом, иначе считывается и записывается как нуль. В документации на версию ARMv7-M сказано, что этот регистр имеется всегда, однако это представляется не очень вероятным, поскольку он не имеет смысла без поддержки отладки.

Атрибуты

- Адрес E000EDF0.

- Небезопасная версия доступна безопасному коду по адресу E002EDF0.

- Регистр не имеет отдельных экземпляров для безопасного и небезопасного состояний.

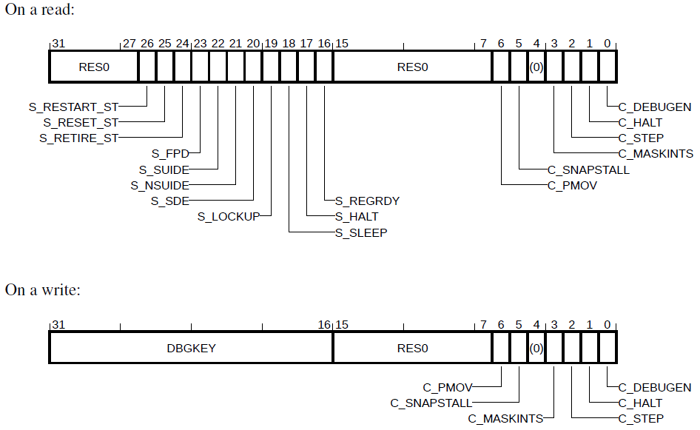

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Ключ доступа к регистру на запись. Должен быть равен A05F, в противном случае запись в регистр игнорируется. | |||

| Этот бит имеется только в ARMv8-M.

Будучи установленным, этот бит показывает, что с момента предыдущего чтения регистра процессор выходил из состояния останова (либо по причине сброса бита C_HALT, либо из-за поступления внешнего запроса на пуск). Если запись нуля в C_HALT производится в момент, когда процессор не находится в состоянии останова, нельзя предсказать, будет ли установлен этот бит. Нельзя предсказать также его значение, если отладка запрещена (бит C_DEBUGEN сброшен). Если одновременно приходят запросы на сброс бита C_HALT и на останов процессора, процессор формально выходит из состояния останова и тут же останавливается вновь, что приводит к установке бита S_RESTART_ST. При чтении этот бит сбрасывается. | |||

| Будучи установленным, этот бит показывает, что с момента последнего чтения регистра DHCSR выполнялся сброс процессора.

При чтении этот бит сбрасывается. Тёплый сброс устанавливает этот бит. | |||

| Будучи установленным, этот бит показывает, что с момента последнего чтения регистра DHCSR процессор выполнил хотя бы одну команду.

При чтении этот бит сбрасывается. После тёплого сброса состояние этого бита непредсказуемо. | |||

Этот бит появился в ARMv8.1-M и показывает, доступны ли отладчику (через регистр DCRSR) в текущем состоянии процессора регистры данных FPU, FPSCR и VPR:

| |||

| Этот бит имеется только в ARMv8.1-M с расширением безопасности и UDE.

Показывает, разрешён ли отладочный останов непривилегированного безопасного кода:

Пока процессор находится в состоянии отладочного останова, этот бит не изменяется. | |||

| Этот бит имеется только в ARMv8.1-M с UDE.

Показывает, разрешён ли отладочный останов непривилегированного небезопасного кода:

Пока процессор находится в состоянии отладочного останова, этот бит не изменяется. | |||

Этот бит имеется только в ARMv8-M с расширением безопасности и показывает, разрешена ли потенциально отладка безопасного кода:

Этот бит не изменяет своё состояние, пока процессор находится в состоянии отладки. | |||

| Единица в этом разряде показывает, что процессор перешёл в состояние блокировки. Когда отладчик выполняет останов процессора, этот бит сбрасывается. | |||

| Единица в этом разряде показывает, что процессор находится в состоянии сна.

Для пробуждения процессора отладчик должен либо дождаться наступления прерывания или пробуждающего события, либо установить бит C_HALT. | |||

| Единица в этом разряде показывает, что процессор находится в остановленном (отладочном) состоянии. | |||

| Этот бит используется для индикации завершения операции чтения или записи регистров процессора через регистр DCRDR: его установленное состояние показывает, что обмен с DCRDR завершён либо не запрашивался.

Если процессор не находится в остановленном состоянии, значение данного бита непредсказуемо. Согласно документации на ARMv8-M, оно непредсказуемо и после тёплого сброса. После тёплого сброса состояние этого бита непредсказуемо. | |||

| Зарезервировано. | |||

Этот бит имеется лишь в ARMv8.1-M с PMU и управляет остановом процессора при переполнении счётчика PMU:

После холодного сброса состояние этого бита непредсказуемо. | |||

| Этот бит может присутствовать только в ARMv8-M с основным расширением, но является необязательным: конкретная реализация может всегда удерживать его сброшенным.

Установка этого бита разрешает неточный вход в состояние отладки — например, путём принудительного прекращения ожидающей завершения команды загрузки или записи. Состояние подсистемы памяти при этом становится непредсказуемым, поэтому отладчик перед выходом из состояния отладки должен выполнить сброс процессора. Поведение процессора непредсказуемо, если одновременно с установкой бита C_SNAPSTALL отладчик не устанавливает биты C_DEBUGEN и C_HALT. Если все три разряда устанавливаются одновременно, а процессор ещё не находится в состоянии отладки, он перейдёт в него сразу после завершения выполнения (в том числе путём принудительного прекращения) текущей команды. Если в процессоре реализовано расширение безопасности и либо бит S_SDE сброшен, либо бит S_SUIDE установлен, запись в этот разряд игнорируется. Если отладочный останов запрещён (в том числе если сброшен бит C_DEBUGEN) или если установлен бит S_NSUIDE, состояние этого разряда игнорируется (процессор считает, что он сброшен). Запись единицы в этот разряд не гарантирует принудительный переход процессора в состояние отладки. Кроме того, не рекомендуется устанавливать этот бит, если процессор уже находится в отладочном состоянии. Холодный сброс очищает этот бит. | |||

| Зарезервировано. | |||

| Этот бит устанавливается для запрета входа в обработчики прерываний внешних, PendSV и SysTick.

Операция записи в регистр, изменяющая состояние этого бита, приводит к непредсказуемым результатам, если не соблюдается одно из следующих условий:

Таким образом, нельзя одной операцией записи обнулять бит C_HALT и изменять значение бита C_MASKINTS. Если имеется расширение безопасности и либо сброшен бит S_SDE, либо установлен бит S_SUIDE, состояние C_MASKINTS не влияет на безопасные прерывания. Если отладочный останов запрещён или если бит S_NSUIDE установлен, состояние этого бита процессором игнорируется. Если бит C_DEBUGEN сброшен, состояние бита C_MASKINTS, полученное при чтении регистра, не определено. После холодного сброса состояние этого бита непредсказуемо. | |||

| Запись единицы в этот разряд разрешает выполнение шага программы (одной команды).

Изменение состояния этого бита приводит к непредсказуемым результатам, если не соблюдается любое из следующих условий:

Состояние этого бита игнорируется, если отладочный останов запрещён либо если при наличии расширения безопасности процессор при сброшенном бите S_SDE находится в безопасном состоянии. Если бит C_DEBUGEN сброшен, состояние бита C_STEP, полученное при чтении регистра, не определено. После холодного сброса состояние этого бита непредсказуемо. | |||

| Запись нуля в этот разряд выводит процессор из состояния отладочного останова, запись единицы вызывает вход в останов.

Процессор сам устанавливает этот бит, если наступает отладочное событие, требующее перехода в останов. Состояние этого бита игнорируется, если:

Если бит C_DEBUGEN сброшен, состояние бита C_HALT, полученное при чтении регистра, не определено. После тёплого сброса этот бит сброшен. | |||

Управление возможностью отладочного останова:

Запись, выполняющая установку этого бита, должна записывать нуль в бит C_MASKINTS, в противном случае последствия непредсказуемы. Когда этот бит сброшен, процессор игнорирует состояние битов C_MASKINTS, C_STEP и C_HALT, а считываемое значение этих трёх битов и бита S_RESTART_ST непредсказуемо. Запись в этот бит может выполняться только отладчиком. Холодный сброс обнуляет этот разряд. |

Регистр программной блокировки доступа к SCS DLAR[]

Назначение

- Даёт возможность программно заблокировать или разрешить доступ программе к регистрам SCS.

Ограничения на использование

- Только привилегированный доступ (отказ при непривилегированном доступе).

- Доступ только к слову (непредсказуемый результат при доступе к полуслову или байту).

- При обращении со стороны отладчика чтение возвращает нуль, запись игнорируется.

Конфигурации

- Присутствует, только если реализована идентификация CoreSight и необязательный механизм программной блокировки. При отсутствии считывается и записывается как нуль.

Атрибуты

- Адрес E000EFB0, доступ только для записи.

- Небезопасная версия доступна безопасному коду по адресу E002EFB0.

- Регистр не имеет отдельных экземпляров для безопасного и небезопасного состояний.

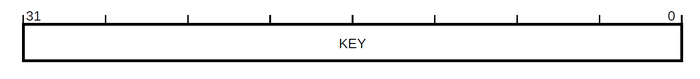

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Запись значения C5ACCE55 снимает блокировку, любого другого — устанавливает её. Пока блокировка активна, любые доступы на запись игнорируются, а доступы на чтение не вызывают побочных эффектов (например, сброса битов, которые обычно сбрасываются при их считывании). |

Из документации остаётся неясным, запрещается доступ только к регистрам управления отладкой (спецификация CoreSight, вообще говоря, подразумевает именно это) или же ко всем регистрам SCS, кроме самого DLAR.

Регистр состояния программной блокировки доступа к SCS DLSR[]

Назначение

- Предоставляет информацию о состоянии программной блокировки доступа программы к SCS.

Ограничения на использование

- Только привилегированный доступ (отказ при непривилегированном доступе).

- Доступ только к слову (непредсказуемый результат при доступе к полуслову или байту).

- При обращении со стороны отладчика чтение возвращает нуль, запись игнорируется.

Конфигурации

- Присутствует, только если реализована идентификация CoreSight и необязательный механизм программной блокировки. При отсутствии считывается и записывается как нуль.

Атрибуты

- Адрес E000EFB4, доступ только для записи.

- Небезопасная версия доступна безопасному коду по адресу E002EFB4.

- Регистр не имеет отдельных экземпляров для безопасного и небезопасного состояний.

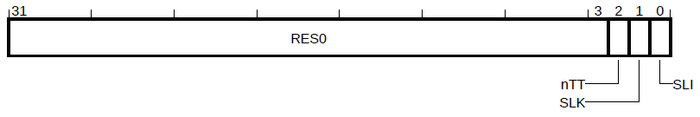

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервировано. | |||

| Всегда равен нулю, указывая, что регистр DLAR является 32-разрядным. | |||

Состояние программной блокировки:

Тёплый сброс обнуляет этот бит. | |||

Признак поддержки возможности программной блокировки:

|

Регистр выбора регистра ядра DCRSR[]

Назначение

- Обеспечивает возможность выбора регистра процессора, доступ к которому будет выполнен через регистр DCRDR.

Ограничения на использование

- Только привилегированный доступ (отказ при непривилегированном доступе).

- Начиная с ARMv8.1-M, регистр доступен для непривилегированных обращений со стороны DAP, если установлен бит DAUTHCTRL.UIDAPEN для любого режима безопасности.

- Доступ только к слову (непредсказуемый результат при доступе к полуслову или байту).

- Запись в регистр, если процессор не остановлен, игнорируется.

- Регистр доступен только для отладчика.

Конфигурации

- Присутствует только при поддержке отладки.

Атрибуты

- Адрес E000EDF4, доступ только для записи.

- Регистр не имеет отдельных экземпляров для безопасного и небезопасного состояний.

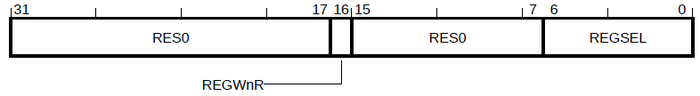

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервировано. | |||

Тип доступа к выбранному регистру:

| |||

| Зарезервировано. | |||

Код выбора регистра:

При записи любого другого кода поведение процессора непредсказуемо. При наличии расширения безопасности регистры FPSCR, VPR и S0–S31 недоступны:

|

Регистр данных регистра ядра DCRDR[]

Назначение

- Обеспечивает доступ к регистру процессора, выбранного через регистр DCRSR.

Ограничения на использование

- Только привилегированный доступ (отказ при непривилегированном доступе).

- Начиная с ARMv8.1-M, регистр доступен для непривилегированных обращений со стороны DAP, если установлен бит DAUTHCTRL.UIDAPEN для любого режима безопасности.

- Доступ только к слову (непредсказуемый результат при доступе к полуслову или байту).

- Регистр доступен только для отладчика.

Конфигурации

- Присутствует только при поддержке отладки.

Атрибуты

- Адрес E000EDF8, доступ только для записи.

- Небезопасная версия доступна безопасному коду по адресу E002EDF8.

- Регистр не имеет отдельных экземпляров для безопасного и небезопасного состояний.

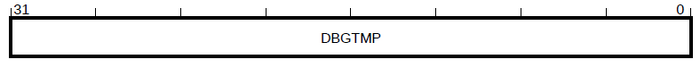

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Буфер данных, обеспечивающий считывание или запись значения выбранного регистра процессора. |

Регистр управления отладочными прерываниями и монитором DEMCR[]

Назначение

- Управляет обработкой прерываний DebugMonitor и обращений к векторам.

Ограничения на использование

- Только привилегированный доступ (отказ при непривилегированном доступе).

- Начиная с ARMv8.1-M, регистр доступен для непривилегированных обращений со стороны DAP, если установлен бит DAUTHCTRL.UIDAPEN для любого режима безопасности.

- Доступ только к слову (непредсказуемый результат при доступе к полуслову или байту). Начиная с ARMv8.1-M, возможен доступ полусловами и байтами.

- В ARMv8-M без основного расширения и ARMv6-M доступность регистра для ПО определяется реализацией. В ARMv8-M с основным расширением и ARMv7-M регистр доступен и для отладчика, и для ПО.

Конфигурации

- В ARMv8-M без основного расширения и ARMv6-M присутствует только при поддержке отладки; в ARMv8-M с основным расширением и ARMv7-M присутствует всегда.

Атрибуты

- Адрес E000EDFC, доступ только для записи.

- Небезопасная версия доступна безопасному коду по адресу E002EDFC.

- Регистр не имеет отдельных экземпляров для безопасного и небезопасного состояний.

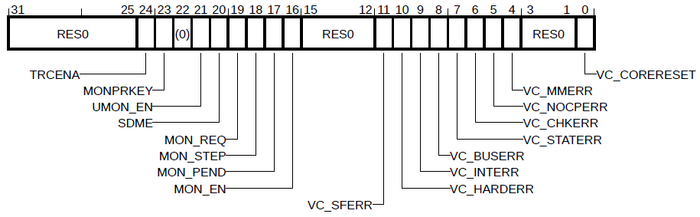

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервировано. | |||

Разрешение трассировки:

Если все три указанных компонента отсутствуют, этот бит всегда равен нулю. Обнуление этого бита не обязательно останавливает генерацию событий. Чтобы гарантировать прекращение их генерации, программа должна сначала обнулить биты управления средствами DWT, PMU и ITM, затем убедиться, что все сгенерированные события удалены из буфера и лишь после этого сбрасывать бит TRCENA. Как этот бит влияет на обработку трассировки, зависит от реализации. ARM рекомендует устанавливать данный бит при использованиии ETM, даже если ни один из трёх перечисленных блоков не используется. В документации на ARMv7-M указывается, что влияние этого разряда на TPIU, ETM и другие компоненты системы, связанные с трассировкой, определяется реализацией. Когда он сброшен, из регистров DWT и ITM будут считываться неопределённые значения, а будет ли при этом игнорироваться запись в указанные блоки, определяется реализацией. Заметим, что PMU в версии ARMv7-M отсутствует. В документации на ARMv6-M этот бит обозначен как DWTENA, что связано с отсутствием в этой версии PMU и ITM. Холодный сброс обнуляет этот бит. | |||

Ключ записи в биты MON_PEND и MON_REQ:

Этот бит появился в ARMv8.1-M. | |||

| Зарезервировано. | |||

Разрешение непривилегированного монитора:

Попытка непривилегированной записи в этот бит со стороны DAP игнорируется. Если бит SDME сброшен, небезопасные обращения на считывание возвращают для данного бита нулевое значение, а небезопасные обращения на запись игнорируются. Этот бит присутствует лишь в ARMv8.1-M с IDE. Тёплый сброс обнуляет этот бит. | |||

Разрешение отладочного монитора для безопасного состояния:

Если имеется ожидающий запрос DebugMon, при считывании этот бит отражает своё значение на момент появления данного прерывания. Если же ожидающий запрос отсутствует, считывание показывает текущее состояние данного бита. Этот бит реализован лишь в ARMv8-M при наличии основного расширения и расширения безопасности. | |||

| Запрос монитора.

Этот бит процессором не используется; он предназначен для обработчика прерывания DebugMon, который может пользоваться им по своему усмотрению. Этот бит отсутствует в ARMv8-M без основного расширения и ARMv6-M. Тёплый сброс очищает этот бит. | |||

Запрос пошагового выполнения программы под управлением обработчика прерывания DebugMon:

Изменение этого бита не должно выполняться, если текущий приоритет выполнения меньше приоритета прерывания DebugMon, в противном случае результат будет непредсказуем. Этот бит отсутствует в ARMv8-M без основного расширения и ARMv6-M. Тёплый сброс очищает этот бит. | |||

Признак ожидающего запроса DebugMon и установка/сброс этого запроса:

Этот разряд управляет состоянием ожидания запроса DebugMon независимо от состояния битов MON_EN и UMON_EN. Этот бит отсутствует в ARMv8-M без основного расширения и ARMv6-M. Тёплый сброс очищает этот бит. | |||

Разрешение прерывания DebugMon:

Если отладочное событие останавливает процессор, значение этого разряда игнорируется. Непривилегированные обращения на запись от DAP не изменяют этот бит. Если бит SDME установлен, небезопасные обращения на чтение и запись к этому разряду игнорируются. Этот бит отсутствует в ARMv8-M без основного расширения и ARMv6-M. Тёплый сброс очищает этот бит. | |||

| Зарезервировано. | |||

Останов по прерыванию SecureFault:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE). Этот бит реализован только в ARMv8-M с основным расширением и расширением безопасности, если при этом поддерживается отладочный останов. Холодный сброс обнуляет этот бит. | |||

Останов по прерыванию HardFault:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE; два последних бита имеются лишь в процессорах с расширением безопасности и вызывают игнорирование состояния VC_HARDERR лишь в случае, если прерывание HardFault адресуется безопасному режиму). Этот бит реализован только при поддержке отладочного останова. Холодный сброс обнуляет этот бит. | |||

Останов по прерываниям, связанным с возникновением отказов при отложенном сохранении контекста FPU, с нарушением границ стека и с сохранением либо восстановлением контекста при входе или выходе из обработчика прерывания:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE; два последних бита имеются лишь в процессорах с расширением безопасности и вызывают игнорирование состояния VC_INTERRлишь в случае, если соответствующее прерывание адресуется безопасному режиму). Этот бит реализован только в ARMv8-M с основным расширением и ARMv7-M, если отладочный останов поддерживается. Холодный сброс обнуляет этот бит. | |||

Останов по прерыванию BusFault:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE; два последних бита имеются лишь в процессорах с расширением безопасности и вызывают игнорирование состояния VC_BUSERR лишь в случае, если прерывание BusFault адресуется безопасному режиму). Этот бит реализован только в ARMv8-M с основным расширением и ARMv7-M, если отладочный останов поддерживается. Холодный сброс обнуляет этот бит. | |||

Останов по прерыванию UsageFault, вызванному неправильной информацией, например, попыткой выполнения несуществующей команды:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE; два последних бита имеются лишь в процессорах с расширением безопасности и вызывают игнорирование состояния VC_STATERR лишь в случае, если прерывание адресуется безопасному режиму). Этот бит реализован только в ARMv8-M с основным расширением и ARMv7-M, если отладочный останов поддерживается. Холодный сброс обнуляет этот бит. | |||

Останов по прерыванию UsageFault, вызванному нарушением выравнивания либо делением на нуль:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE; два последних бита имеются лишь в процессорах с расширением безопасности и вызывают игнорирование состояния VC_CHKERR лишь в случае, если прерывание адресуется безопасному режиму). Этот бит реализован только в ARMv8-M с основным расширением и ARMv7-M, если отладочный останов поддерживается. Холодный сброс обнуляет этот бит. | |||

Останов по прерыванию UsageFault, вызванному недопустимой попыткой доступа к сопроцессору:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE; два последних бита имеются лишь в процессорах с расширением безопасности и вызывают игнорирование состояния VC_NOCPERR лишь в случае, если прерывание адресуется безопасному режиму). Этот бит реализован только в ARMv8-M с основным расширением и ARMv7-M, если отладочный останов поддерживается. Холодный сброс обнуляет этот бит. | |||

Останов по прерыванию MemManage:

Значение этого разряда игнорируется, если отладочный останов запрещён вообще (соответствующим внешним сигналом либо сброшенным битом DHCSR.C_DEBUGEN) либо если запрещён останов привилегированного кода (установлен любой из битов DHCSR.S_NSUIDE или DHCSR.S_SUIDE либо сброшен бит DHCSR.S_SDE; два последних бита имеются лишь в процессорах с расширением безопасности и вызывают игнорирование состояния VC_MMERR лишь в случае, если прерывание адресуется безопасному режиму). Этот бит реализован только в ARMv8-M с основным расширением и ARMv7-M, если отладочный останов поддерживается. Холодный сброс обнуляет этот бит. | |||

| Зарезервировано. | |||

Останов по тёплому сбросу:

Значение этого разряда игнорируется, если отладочный останов запрещён битом DHCSR.C_DEBUGEN. Если же такого запрета нет, установка этого бита и последующий тёплый сброс вызывают появление отладочного события, что приведёт к останову процессора сразу же при входе им в состояние, для которого отладочный останов разрешён. Этот бит реализован только если отладочный останов поддерживается. Холодный сброс обнуляет этот бит. |

Регистры компонентов CoreSight[]

Каждое отладочное устройство, соответствующее спецификации идентификации периферии ARM (ARM peripheral identification specification), имеет набор регистров идентификации, занимающих последние 8 или 12 слов последнего 4-килобайтового блока, выделенного данному устройству. Различают регистры идентификации компонента (CIDR) и регистры идентификации периферийного устройства (PIDR). Все регистры идентификации доступны только на чтение только полными выровненными словами. Их расположение в последнем блоке адресного пространства устройства показано в следующей таблице.

| Смещение | Обозначение | Значение |

|---|---|---|

Регистры PIDR4–PIDR7 отсутствовали в ранних компонентах, а формат регистров PIDR0–PIDR3 у них отличался от современного. Подробнее это описано ниже в соответствующем подразделе.

В зависимости от класса компонента (определяется содержимым разрядов CIDR1[7:4]) компонент имеет те или иные дополнительные стандартные регистры, описанные в следующих подразделах:

- класс 1 — Таблица ПЗУ;

- класс 9 — Компоненты CoreSight;

- класс F — Компоненты CoreLink/PrimeCell и системные компоненты.

Регистры идентификации компонента CIDR0–CIDR3[]

Концептуально компонент идентифицируется 32-разрядным значением, каждый байт которого хранится в младшем байте соответствующего регистра CIDR, как показано на рисунке. Старшие три байта каждого из регистров не используются и содержат нули.

Биты CIDR1[7:4] указывают класс компонента, все остальные разряды идентификатора имеют одно и то же значение, являющееся сигнатурой устройства, соответствующего спецификации ARM CoreSight. Возможные значения указанных битов перечислены в следующей таблице.

| Значение | Описание |

|---|---|

| Общий компонент верификации | |

| Таблица ПЗУ | |

| зарезервировано | |

| Отладочный компонент | |

| зарезервировано | |

| Блок тестирования периферии (PTB) | |

| зарезервировано | |

| Компонент DESS (OptimoDE Data Engine SubSystem) | |

| Общий компонент IP | |

| Периферийное устройство CoreLink (ранее использовалось название PrimeCell) или системный компонент |

Для классов 1 и 9 (таблицы ПЗУ и отладочные компоненты) спецификация CoreSight определяет требования к регистрам идентификации периферийного устройства. Для остальных классов эти требования, если имеются, задаются соответствующими спецификациями.

Регистры идентификации периферийного устройства PIDR0–PIDR7[]

Новые устройства[]

Подобно регистрам CIDR, младшие байты регистров PIDR формируют 64-разрядный идентификатор периферийного устройства, большая часть разрядов которого образует фиксированную сигнатуру. Отображение байтов PIDR на значение идентификатора показано на рисунке.

В следующей таблице описано назначение непостоянных разрядов идентификатора периферийного устройства для случая, когда флаг PIDR2.JEDEC (бит 3 регистра PIDR2) установлен, что соответствует современным устройствам.

| Биты | Обозначение | Описание |

|---|---|---|

| Количество блоков по 4 Кбайта в адресном пространстве данного устройства, выраженное степенью двойки (нуль соответствует одному блоку, единица — двум, двойка — четырём и т. д.). | ||

| Идентификатор разработчика данного компонента. Для компонентов, разработанных ARM, эти поля содержат следующие значения: 0100 (PIDR4.DES_2), 011 (PIDR2.DES_1) и 1011 (PIDR1.DES_0). | ||

| Номер ревизии производителя. Изначально устанавливается равным нулю и увеличивается по мере внесения исправлений в оборудование. | ||

| Номер модификации, внесённой в приобретённое IP-ядро устройство самим покупателем. Если покупатель лишён такой возможности, это поле всегда содержит нуль. | ||

| Версия (ревизия) устройства. Отсчёт начинается с нуля. | ||

| Флаг использования идентификационного кода JEP106, для современных устройств всегда установлен. Когда этот бит сброшен (в старых устройствах), регистры PIDR4–PIDR7 отсутствуют, а формат регистров PIDR0–PIDR3 отличается от показанного на рисунке выше и описываемого данной таблицей. | ||

| Номер компонента (part number), присваиваемый его разработчиком. Для компонентов класса 9 (отладочные компоненты) допустимо использовать один и тот же номер для разных компонентов при условии, что они имеют разный тип устройства (DEVTYPE). Тем не менее, рекомендуется каждому компоненту присваивать уникальный номер. |

Старые устройства[]

Старые устройства (флаг PIDR2.JEDEC, т. е. бит PIDR2[3], сброшен) могут использовать смещения FD0–FDC, в которых в новых устройствах находятся регистры PIDR4–PIDR7, по своему усмотрению. Регистры PIDR0–PIDR3 таких устройств содержат поля, описанные в следующей таблице. Как и в случае новых устройств, используются только младшие байты регистров, три старших байта каждого регистра зарезервированы и должны быть равны нулю.

| Биты | Описание |

|---|---|

| Присвоенный разработчиком номер компонента (part number), разряды 7:0. | |

| ASCII-идентификатор разработчика, разряды 3:0. Для ARM это поле равно 0001. | |

| Присвоенный разработчиком номер компонента, разряды 11:8. | |

| Номер версии (ревизии) устройства. | |

| Флаг типа идентификатора разработчика, равен нулю. | |

| ASCII-идентификатор разработчика, разряды 6:4. Для ARM это поле равно 100. | |

| Регистр конфигурации, описывающий параметры, использованные при построении данного устройства. Например, он может отражать ширину шины, для которой собрано устройство. |

Компоненты CoreSight[]

Стандартные регистры компонентов CoreSight[]

Все отладочные компоненты CoreSight имеют класс компонента 9 и располагают, помимо регистров идентификации, следующим набором стандартных регистров, находящихся в конце последнего блока адресного пространства, занимаемого данным компонентом.

| Смещение | Доступ | Обозначение | Назначение |

|---|---|---|---|

| Регистр управления режимом интеграции | |||

| Claim Tag Set register | |||

| Claim Tag Clear register | |||

| Регистр 0 сродства устройства | |||

| Регистр 1 сродства устройства | |||

| Регистр блокирующего доступа | |||

| Регистр состояния блокировки | |||

| Регистр состояния аутентификации | |||

| Регистр архитектуры устройства | |||

| Регистр 2 конфигурации устройства | |||

| Регистр 1 конфигурации устройства | |||

| Регистр конфигурации устройства | |||

| Регистр идентификации типа устройства |

Регистр ITCTRL[]

Регистр CLAIMSET[]

Регистр CLAIMCLR[]

Регистры DEVAFF[]

Регистр LOC[]

Регистр LSR[]

Регистр AUTHSTATUS[]

Регистр DEVARCH[]

Регистры DEVID[]

Регистр DEVTYPE[]

Блок трассировки и слежения за данными (DWT)[]

Блок точек останова (BPU)[]

Таблица ПЗУ[]

Содержимое таблицы ПЗУ позволяет отладчику убедиться в наличии или отсутствии тех или иных отладочных средств и получить необходимые базовые адреса.

Система может содержать несколько таблиц ПЗУ, каждая из которых занимает 4 Кбайта и размещена на соответствующей границе. Попытки записи в таблицу ПЗУ игнорируются.

Общий формат таблицы ПЗУ выглядит следующим образом:

| Смещение | Размер | Обозначение | Описание |

|---|---|---|---|

| Элементы таблицы размером 4 байта каждый | |||

| Зарезервированная область | |||

| Регистр MEMTYPE | |||

| Регистры идентификации периферийного устройства | |||

| Регистры идентификации компонента |

Таблицы ПЗУ могут образовывать иерархию, однако на одну и ту же таблицу не может ссылаться несколько других таблиц. Абсолютный адрес таблицы самого верхнего уровня доступен отладчику через предназначенный для этого регистр отладочного порта. Программа, выполняемая процессором, не имеет доступа к этому регистру, поэтому, если ей необходим доступ к таблицам, адрес таблицы верхнего уровня должен быть задан программистом вручную (что делает программу привязанной к конкретной модели процессора).

Элементы таблицы[]

Каждый элемент таблицы является 32-разрядным словом и описывает один отладочный компонент. Его разряды имеют следующее назначение:

| Биты | Название поля | Описание |

|---|---|---|

| Это поле определяет адрес последнего 4-килобайтового блока адресов, относящихся к компоненту, относительно адреса начала данной таблицы ПЗУ и представляет из себя число со знаком. Базовый адрес компонента равен сумме базового адреса таблицы ПЗУ и значения этого поля, дополненного справа двенадцатью нулями.

Это поле не должно быть равно нулю даже при нулевом значении бита 0 (элемент не используется), за исключением завершающего элемента таблицы. | ||

| Зарезервировано | ||

| Определяет домен питания, к которому относится данный компонент. Это поле поддерживает до 32 доменов и действительно только в случае, если бит 2 установлен; в противном случае это поле содержить нуль | ||

| Зарезервировано | ||

| Этот бит указывает, корректен ли идентификатор домена питания в разрядах 8:4. Идентификатор корректен, когда этот разряд установлен | ||

| Этот бит всегда установлен | ||

| Когда установлен, этот бит показывает, что данный элемент используется |

Отладочный компонент имеет адресное пространство, состоящее из целого числа 4-килобайтовых блоков. Поле смещения в элементе таблицы ПЗУ позволяет получить адрес последнего из этих блоков. В конце данного блока (начиная со смещения FD0) располагаются регистры идентификации периферийного устройства и компонента (PID и CID), позволяющие однозначно определить тип данного компонента. Число 4-килобайтовых блоков, занимаемых компонентом, определяется битами PID4[4:7] (их нулевое значение соответствует одному блоку).

Таблица может содержать до 960 элементов включительно. Если реально элементов меньше, сразу после последнего элемента должен следовать элемент, содержащий нули во всех разрядах. Заметим, что используемые элементы могут перемежаться с неиспользуемыми (содержащими нуль в младшем разряде); само по себе появление неиспользуемого элемента не является признаком конца используемых элементов.

Элемент может указывать на другую таблицу ПЗУ. Таким образом, возможно построение иерархии таблиц.

Если в таблице имеются элементы, содержащие идентификатор домена питания (установлен бит 2 хотя бы в одном из используемых элементов), требуется наличие так называемого запросчика питания (power requestor), которому должна соответствовать своя запись таблицы. Эта запись не должна содержат идентификатор домена, а сам запросчик должен входить в тот же домен, что и таблица. Это позволяет отладчику с помощью таблицы найти запросчик и включить питание требуемого домена.

Регистр MEMTYPE[]

Регистр MEMTYPR содержит только один значащий разряд — бит 0:

- когда бит 0 сброшен, это означает, что все допустимые адреса на шине, на которой находится таблица ПЗУ, описаны этой таблицей. Попытка обратиться к другим адресам приведёт к непредсказуемым последствиям;

- когда бит 1 установлен, это означает, что на шине определены области адресов, не описываемые таблицей ПЗУ. Положение, размеры и типы этих областей определены какими-либо стандартными средствами быть не могут. Предполагается, что отладочное ПО способно установить карту памяти, опираясь, например, на предоставленную пользователем информацию о конкретном типе процессора.