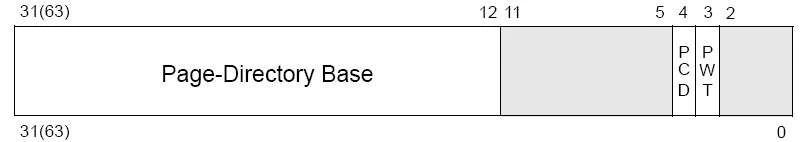

Управляющий регистр CR3 впервые появился в микропроцессоре 80386. Он содержит физический адрес каталога страниц или таблицы указателей каталогов страниц, а также два флага. Его формат показан на рисунке:

Назначение разрядов регистра CR3 описано ниже.

| PWT | Прозрачная запись в таблицы страниц (бит 3). Управляет политикой сквозной или обратной записи из кэша для текущего каталога страниц. Когда флаг PWT установлен, разрешено кэширование со сквозной записью; когда он сброшен, разрешено кэширование с обратной записью. Этот флаг влияет только на внутренние кэши (L1 и L2, если они имеются). Процессор игнорирует этот флаг, если страничный режим не используется (флаг PG регистра CR0 сброшен) или же если кэширование запрещено (установлен флаг CD регистра CR0). |

| PCD | Запрет кэша уровня страниц (бит 4). Управляет кэшированием текущего каталога страниц. Когда флаг PCD установлен, кэширование каталога страниц запрещается, когда сброшен — разрешается. Этот флаг влияет только на процессоры, обладающие внутренним кэшем (и L1, и L2, если присутствуют оба). Процессор игнорирует этот флаг, если страничный режим не включен (флаг PG регистра CR0 сброшен) или же если установлен флаг CD регистра CR0 (запрет кэширования). |

| PDB | Базовый адрес каталога страниц (биты 63–12 или 31–12). В этом поле содержатся старшие разряды физического базового адреса каталога страниц или таблицы указателей каталогов страниц. Младшие 12 разрядов считаются равными нулю. |